PWM Operation for 2806

Submitted by Joe on Wed, 05/02/2012 - 04:11

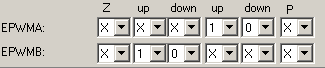

I was hoping you can clarify something for me. In your ePWM block for the 2806 you have an input which is % Duty Cycle A(1.16). Can you define what you mean by this? Since this ePWM module uses an Action Qualifier I’m not sure what you mean by 0% or 100% duty cycle. Our block for the ePWM is as below:

.png.8e206d990a576511223700146b33c154.png)

So if I set % Duty Cycle A(1.16) input to 100% (actually 0.99997) does this mean CMPA will hit at the start of the up count and the end of the down count OR will it hit near the top of the up count and near the top of the down count?

Thanks

Bruce

Answers

-

Submitted by Anders89 on Wed, 05/02/2012 - 05:19.

The '%duty cycle A' block input gives the fraction of the period that will be assigned to the compare register CMPA, '%duty cycle B'. Since we use the input fx1.16 (1 magnitude bit in a 16 bit word), and the top bit is used for the sign, the biggest number you can have in that format is, as you stated, .99997 (which corresponds to the hex value 0x7fff). So lets say we use .9 as the input value. The CMPA = .9*PERIOD. Assuming up/down counting (there would be no down match if we did up count only), according to your Action Qualifer settings above, EPWMA output pin is set by the top row configuration, which says set output to 0 on CMPA up match (near the top of the count) and set it to 1 on CMPA down match (also near the top of the count). So the output A pin will be on for 90% of the time.

The bottom row of Action Qualifier configures the B pin output. In the case above, the B output will correspond to the setting on the '%duty cycle B', so if we use .2 on the '%duty cycle B', we will see 20% duty cycle on the chips PWM B pin.

Note that the 'duty cycle' nomenclature is a bit misleading as it really regulates the % of period that is assigned to the respective compare register.

Consider the following Action Qualifier:

Here we have PWM output pin A being modulated by compare reg CMPB, and output pin B is modulated by CMPA. So a block input value on '%duty cycle A' of .9 will give a PWM output B duty cycle of 10%, and a block input value on '%duty cycle B' of .2 will give a duty cycle of 80% on PWM output pin A.

One more important point, if the Dead-band unit is enabled, then the dead-band mode stands between the action qualifier and the chip pins and the PWM B result from the Action Qualifier is ignored. Using notation PWMA-in as the result of the Action Qualifer fed to the Dead-band unit, the dead-band modes affect outputs in the following way:

mode PWM A output PWM B output Active High Complementary PWMA-in ! PWMA-in Active Low Complementary ! PWMA-in PWMA-in Active High PWMA-in PWMA-in Active Low ! PWMA-in ! PWMA-in Note that in all cases above a Rising Edge Delay Counter delays the turn on of PWM-Aout and a Falling Edge Delay Counter delays the turn off PWM-Bout, and both are activated only by PWM-Ain

0